0

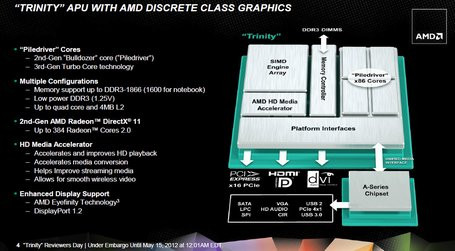

Rappelons que pour AMD, une APU (ou Application Porcessing Unit) regroupe sur une même puce des cœurs d'exécution x86 et un circuit graphique de classe Radeon. A son lancement Llano n'avait pas franchement convaincu. La partie processeur était pour le moins poussive et seul le graphique semblait tenir la route et causer quelques soucis à Intel.

Aujourd'hui les APU A8 et A10, nom de code Virgo, étrennent une toute nouvelle architecture processeur héritée du Bulldozer des AMD FX alors que la partie graphique a elle aussi évolué. Les avancées proposées par AMD pour ces processeurs entrée de gamme ont-elles de quoi inquiéter Intel et ses récents processeurs Core i3 à architecture Ivy Bridge ? Voilà l'une des questions qui nous animera pour ce dossier !

Une architecture processeur qui évolue : place à Piledriver

Lorsqu'AMD a lancé ses processeurs AMD FX il y a plusieurs mois de cela, la surprise a été de taille et il ne faut pas se leurrer, nous parlons bien ici d'une mauvaise surprise. Attendue de longue date, l'architecture Bulldozer s'est avérée bien en deçà des attentes et n'a pas permis le moins du monde à AMD de taquiner son rival de toujours. Si nous nous épanchons sur Bulldozer, c'est que les nouvelles APU Virgo proposées par AMD font fit de leur architecture x86 héritée du K10 pour adopter des cœurs Piledriver ! Face à la génération Llano, le changement est donc conséquent.

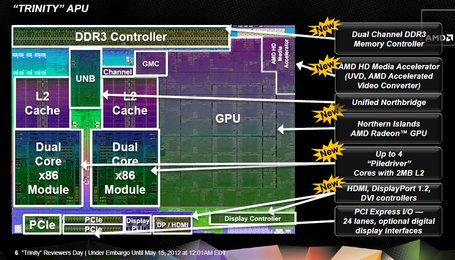

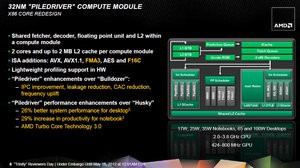

Piledriver incarne ici une évolution de l'architecture Bulldozer. Et comme nous l'avions déjà évoqué lors de notre papier consacré à Trinity sur mobile (voir AMD Trinity : un Bulldozer dans un portable ?), les évolutions si elles sont bien réelles sont plutôt subtiles, du moins par rapport à Bulldozer. Rappelons au passage qu'avec Bulldozer, AMD introduit la notion de module. Chaque module est composé de deux cœurs d'exécution x86 et l'intérêt premier de ce concept est de partager un certain nombre de ressources communes entre les cœurs d'un même module, ce qui est censé conduire à une architecture plus efficace et moins pachydermique en terme de transistors. Tout en donnant à la marque la possibilité de décliner son architecture avec plus ou moins de modules et donc plus ou moins de cœurs.

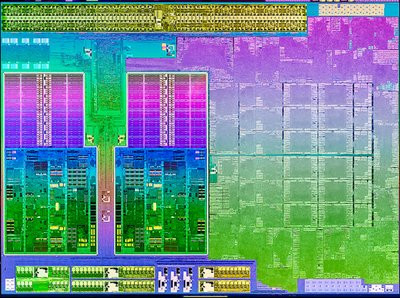

Reste que pour ses APU Virgo, AMD retient un design quadri-cœurs fait de deux modules Piledriver. Au sein d'un module Piledriver, chaque cœur x86 dispose de son propre cache L1, le cache de second niveau étant partagé entre les cœurs. L'agencement du cache est donc différent, mais pas nécessairement sa taille puisque l'on retrouvait dans Llano un cache de second niveau de 1 Mo par cœur, soit 4 Mo au total, alors que Virgo propose 2 Mo de cache L2 par module soit là aussi un total de 4 Mo. Rappelons dans tous les cas l'absence de cache de troisième niveau.

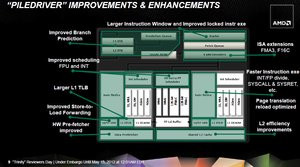

Dans sa documentation technique, AMD évoque foultitude de changements au niveau de l'architecture sans toutefois franchement rentrer dans le détail. On notera l'ajout de certaines instructions notamment pour prendre en charge les calculs FMA3 pour le Fuse/Multiply/Add sur trois opérandes ou les instructions de conversion F16C. Et cela s'ajoute évidemment au tronc commun Bulldozer comme la prise en charge des instructions AVX ou de l'AES-NI.

AMD annonce par ailleurs avoir amélioré les mécanismes de prédiction de branchement ou encore le scheduling alors que l'efficacité du cache de second niveau serait supérieure. Et tout cela dans le but d'offrir un meilleur IPC (nombre d'instructions traitées par cycle d'horloge).

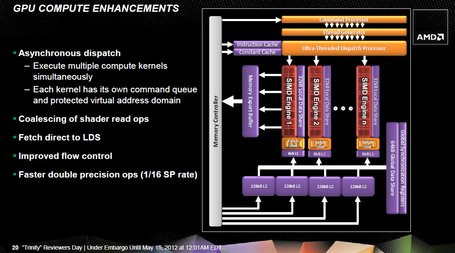

Une partie graphique qui évolue plus timidement

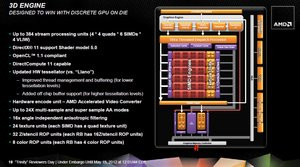

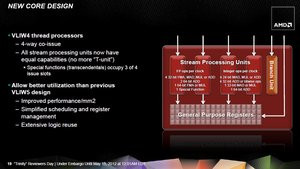

Côté graphique, AMD revoit également sa copie et fait évoluer l'architecture Radeon de son APU pour adopter le design étrenné avec Cayman. En clair, la partie graphique de ces nouvelles APU est dorénavant un dérivé des anciennes Radeon HD 6900 (voir à ce sujet AMD Radeon HD 6950/6970: Nouveau haut de gamme DX11). Face à Llano, cela implique le passage d'une architecture de type VLIW (Very Large Instruction Word) 5 à VLIW 4. Dans sa version la plus évoluée, la partie graphique de Virgo comporte 384 processeurs de flux.

Pour autant, et alors que l'architecture graphique de ses nouvelles APU a une génération de retard par rapport à ce que propose AMD sur ses propres cartes graphiques de bureau, le marketing est passé par là... La partie graphique de APU A8 et A10 est baptisée Radeon HD 7500/7600 alors qu'elle n'a rien de commun avec l'architecture Graphic Core Next des Radeon HD 7000. Reste que naturellement l'ensemble est compatible DirectX 11 et qu'AMD propose quelques évolutions fonctionnelles.

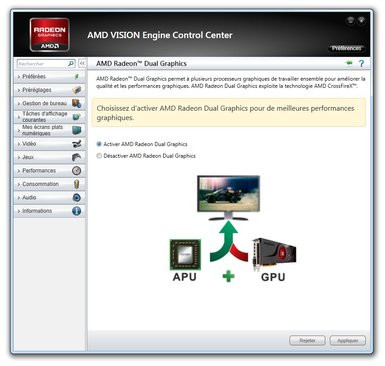

Citons notamment la prise en charge de la technologie EyeFinity pour gérer simultanément trois affichages (jusqu'à 4 avec un hub), la compatibilité DisplayPort 1.2 ou encore quelques améliorations apportées à la fonction Dual Graphics. Rappelons que cette dernière permet d'utiliser conjointement une carte graphique traditionnelle avec le cœur graphique de l'APU et ce dans le but d'améliorer les performances notamment. Attention toutefois, le Dual Graphics ne fonctionne qu'avec des Radeon de génération semblable au cœur graphique de Virgo. Du coup, il n'est pas possible par exemple d'activer cette fonctionnalité avec une Radeon HD 7950v2. Pas de souci à l'inverse avec notre Radeon HD 6670.

Activation de la fonction Dual Graphics depuis les pilotes CATALYST

Like a Virgo : les processeurs A8-5600K et A10-5800K

Pour ce test AMD nous a fait parvenir deux processeurs Virgo, les A8-5600K et A10-5800K. Il s'agit ici du haut du panier de la nouvelle offre d'AMD puisque nous sommes en présence de deux modèles quadruple-coeurs. Sachez en effet qu'AMD décline également ses nouvelles APU en modèle double cœur avec les familles A6 et A4.

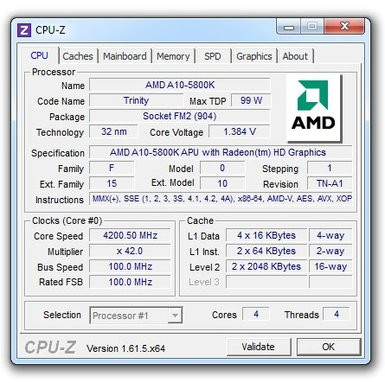

Les processeurs restent gravés en 32nm SOI par GlobalFoundries et AMD annonce 1,3 milliard de transistors pour une surface de die de 246mm². Le processeur A10-5800K est le porte-étendard de cette nouvelle génération d'APU et propose une fréquence de fonctionnement de 3,8 GHz avec un Turbo à 4,2 GHz quand le cœur graphique tourne à 800 MHz, le TDP étant annoncé à 100 Watts. Le modèle A8-5600K tourne à 3,6 GHz avec un Turbo à 3,9 GHz alors que son cœur graphique mouline à 760 MHz pour un TDP identique de 100 Watts.

On notera ici l'augmentation des fréquences assez frappante face à Llano dont le modèle le plus véloce, le A8-3870K, tournait à 3,0 GHz. Qui plus est, l'arrivée du Turbo est une nouveauté sur ses APU, alors que cette technologie est opérationnelle aussi bien côté processeur que sur la partie graphique.

L'A10-5800K vu par CPU-Z

Mais si vous pensiez que ces nouvelles APU allaient être pin-to-pin compatible avec les anciennes Llano... Erreur ! AMD profite effectivement de la sortie de Virgo pour introduire un nouveau Socket, le FM2. Et comble du comble, ce nouveau socket est incompatible avec le FM1 des précédentes APU. AMD serait-il en train de copier les travers d'Intel ? Peut-être, mais en attendant la marque promet qu'elle conservera le socket FM2 au moins pour la génération suivante... À voir !

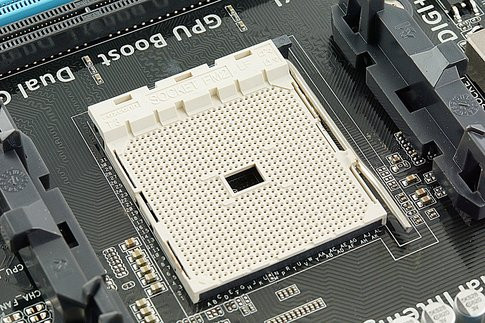

Le nouveau socket AMD FM2, incompatible avec tous les précédents sockets

Enfin, modèle K oblige, les APU A8-5600K et A10-5800K disposent d'un coefficient multiplicateur débloqué, ce qui facilite leur overclocking.

Intel Core i3 Ivy Bridge

De son côté, Intel a pris son temps mais a finalement décliné son architecture Ivy Bridge sur l'entrée de gamme avec l'avènement des processeurs Core i3 de la série 3000. Ces processeurs gravés en 22 nm et présentés au format Socket LGA-1155 se caractérisent par leur nombre de cœurs. Alors qu'AMD aligne sur presque toutes ses nouvelles APU quatre cœurs, le fondeur de Santa-Clara ne propose que deux cœurs avec ses Core i3 Ivy Bridge. Sur le papier Intel est donc handicapé... Oui mais voilà, les Core i3 en question profitent de l'HyperThreading qui permet à chaque cœur de travailler sur deux threads. Côté mémoire, Intel propose un contrôleur double canal opérant avec de la DDR3 1600 Mhz.

Autre atout pour ces Core i3, la présence de mémoire cache de troisième niveau à hauteur de 3 Mo qui s'ajoute au cache L2 de 256 Ko par coeur. En ce qui concerne les jeux d'instructions pris en charge, Intel procède à quelques coupes... sombres ! Ainsi l'AES-NI que gèrent pourtant les processeurs AMD n'est pas de la partie. Côté fréquences de fonctionnement, pas de bouleversement chez Intel, nous avons droit à 3,3 GHz pour le Core i3 3220 ou encore 3,4 GHz pour le Core i3 3240, le plus rapide des Core i3 actuellement commercialisés. Puisque nous parlons fréquence, précisons que les Core i3 ne profitent pas de la technologie Turbo Boost d'Intel. Sachez également que les Core i3220, Core i3 3225 et Core i3 3240 sont annoncés pour un TDP, ou enveloppe thermique, de 55 Watts.

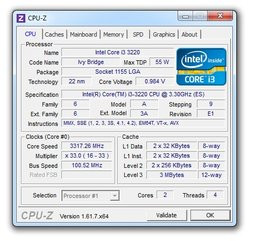

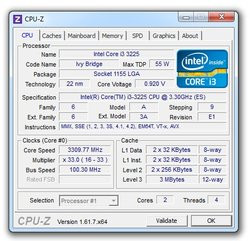

Intel Core i3 3220 et Core i3 3225 vus par CPU-Z

Côté cœur graphique embarqué, en fonction du modèle de Core i3, on a droit à un cœur graphique HD 2500 ou HD 4000. Alors que la fréquence de fonctionnement des circuits HD Graphics est identique d'un modèle à l'autre, 650 MHz avec une pointe à 1,05 GHz si nécessaire, leur nombre d'unités de calcul diffère. Le HD 4000 peut s'appuyer sur 16 unités contre 6 pour le HD 2500 et dans tous les cas DirectX 11 est pris en charge.

L'Intel HD Graphics 2500 vu par les pilotes Intel

Intel Pentium G Ivy Bridge

À noter qu'Intel propose dans une gamme de prix encore inférieure une déclinaison de ses processeurs Core i3 avec le Pentium G. C'est ainsi que nous avons pu mettre la main sur le Pentium G 2120, un processeur double cœur dépourvu d'HyperThreading mais bénéficiant tout de même des dernières nouveautés d'Intel comme l'architecture Ivy Bridge ou la finesse de gravure en 22 nm. Cadencé à 3,1 GHz, sans Turbo, ce modèle dispose également de 3 Mo de mémoire cache de troisième niveau. Il embarque un cœur graphique baptisé simplement Intel HD Graphics et cadencé aux mêmes fréquences que celui des Core i3 variant de 650 MHz à 1,05 GHz. En réalité, et bien que le marketing d'Intel ne semble pas l'assumer, il s'agit ni plus ni moins que d'un HD 2500.

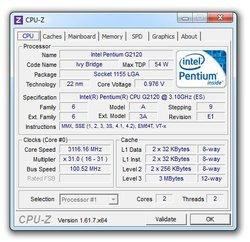

Intel Pentium G 2120 vu par CPU-Z

- Carte mère Asus F2A85-M Pro,

- 4x 4 Go mémoire DDR3-1866 Corsair @1866MHz,

- SSD Corsair Neutron GTX 240 Go + Intel 520 Series 60 Go,

- Carte graphique AMD Radeon HD 7950 v2

- Carte mère Asus F1A75V-Pro

- 4x 4 Go mémoire DDR3-1866 Corsair @1866 MHz

- SSD Corsair Neutron GTX 240 Go + Intel 520 Series 60 Go,

- Carte graphique AMD Radeon HD 7950 v2

- Carte mère Asus P8Z77 Deluxe,

- 4x 4 Go mémoire DDR3-1866 Corsair @1866MHz,

- SSD Corsair Neutron GTX 240 Go + Intel 520 Series 60 Go,

- Carte graphique AMD Radeon HD 7950 v2

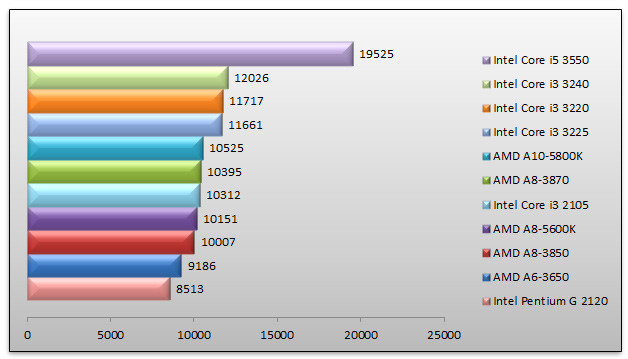

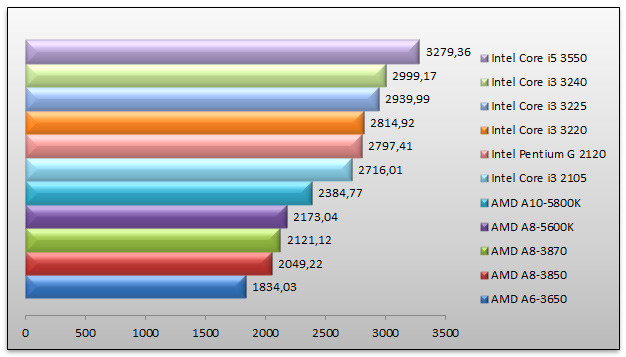

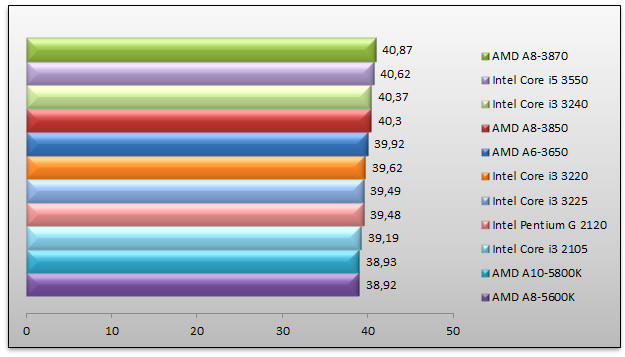

3DMark Vantage - v1.0.1 - Test processeur

Classique qu'on ne présente plus, 3DMark Vantage donne la pôle position au Core i5 3550 et de loin. Première surprise, le plus rapide des Virgo, l'APU A10-5800K est ici 1,2% plus rapide que la plus rapide des APU Llano, l'A8-3870. Pas de quoi pavoiser donc. Les processeurs Core i3 sont tous plus rapides et le Core i3 3220 se montre ainsi 15% plus rapide que le tout nouveau A8-5600K. Carton rouge pour le Pentium G 2120 qui termine bon dernier.

PCMark 7

La suite de test PCMark ne remet pas en cause l'avantage très net du Core i5 3550 sur les autres processeurs. Les Core i3 confirment ici une certaine suprématie et seul l'A10 5800K d'AMD parvient à taquiner le Core i3 3220. Face à la première génération d'APU, autrement dit face au processeur Llano A8-3850, la nouvelle APU A8-5600K est 11% plus rapide. Quant à l'écart de performances entre nos deux représentants de la famille Virgo il est de 3%. A noter que le Pentium G 2120 fait ici mieux que les APU de première génération d'AMD et devance d'un cheveu le Core i3 2105 de génération Sandy Bridge !

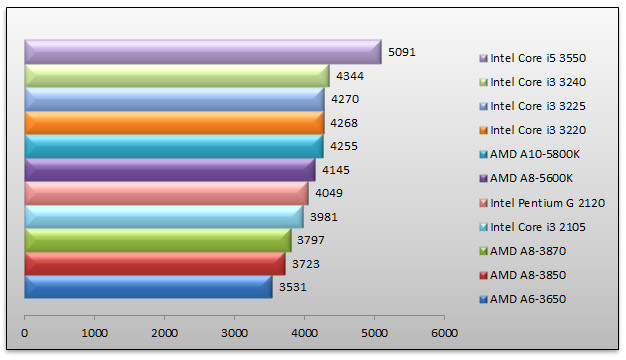

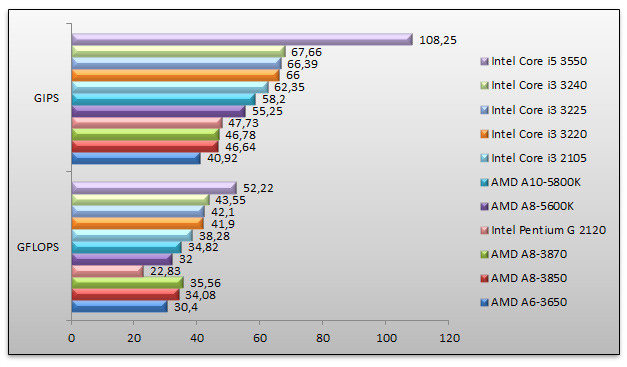

Sandra 2012 - Test processeur

Le test processeur de Sandra 2012 confirme les très bonnes aptitudes de l'architecture Intel à délivrer le plus grand nombre d'instructions par seconde. Seul le Pentium G avec ses deux coeurs d'exécution est ici mis en défaut. Les nouvelles APU d'AMD ne parviennent pas à taquiner les Core i3 Ivy Bridge, même si l'on observe un gain certain face à la génération précédente, de l'ordre de 24% quand même en ce qui concerne les GIPS.

ScienceMark 2.0 x64 - Primordia

ScienceMark confirme les très bonnes performances des processeurs Intel. Alors que le Core i5 3550 domine le classement, même le Pentium G fait mieux que les APU d'AMD. L'A10 se montre tout de même 12% plus rapide que la génération précédente ici représentée par l'A8-3870. Le Core i3 3220 d'architecture Ivy Bridge affiche ici des performances 4% supérieures à son prédécesseur Sandy Bridge, le Core i3 2105.

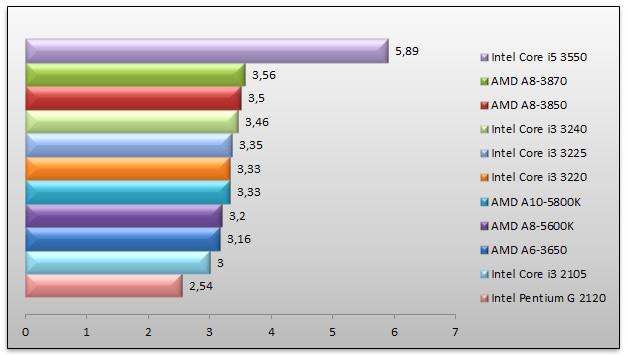

Cinebench 11.5

Cinebench et son célèbre test de rendu 3D fait la part belle au Core i5 3550 qui demeure tout simplement intouchable. Il est intéressant de constater qu'ici les APU de première génération, autrement dit les Llano, sont plus rapides que les nouveaux Virgo... Sans que nous puissions vous l'expliquer. L'A10-5800K, nouveau fleuron de la gamme d'APU d'AMD, fait donc jeu égal avec le Core i3 3220.

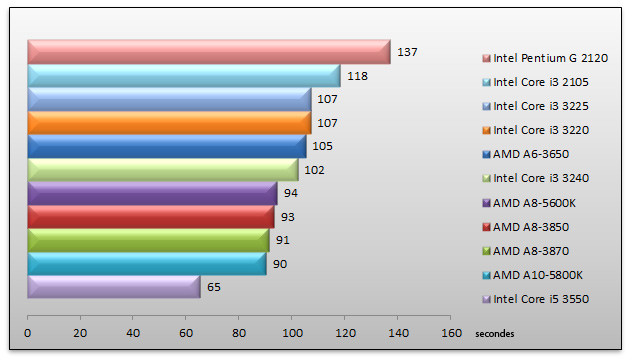

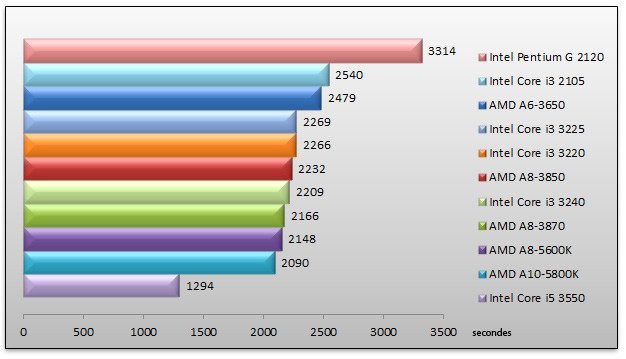

Compression de fichiers - WinRAR 4.20

Nous mesurons ici le temps nécessaire pour créer une archive à partir d'un set de fichiers. Les résultats sont exprimés en secondes, la barre la plus courte représente le processeur le plus rapide qui... sans surprise est le Core i5 3550. Les Core i3 et même le Pentium G affichent ici un avantage certain sur les processeurs AMD. Ainsi quand il faut plus de 50 secondes aux APU Llano pour générer notre archive, le Core i3 3220 s'affranchira de la même tâche en une dizaine de secondes de moins et ce de SSD à SSD. Qui plus est les performances des APU Virgo sont ici inférieures à celles de leurs homologues Llano de précédente génération.

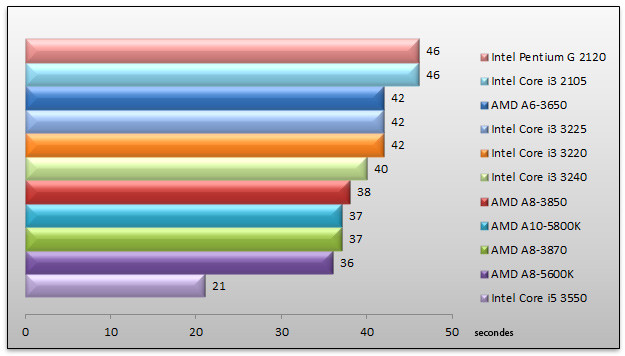

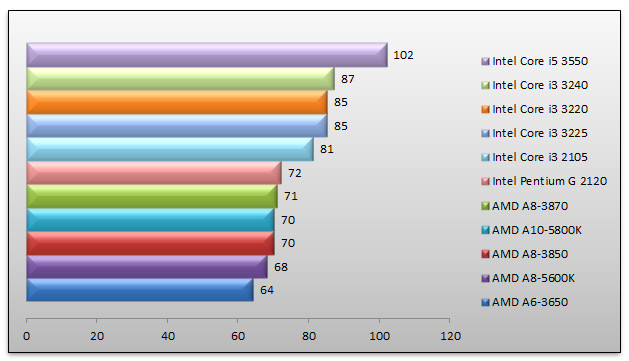

3DSMax 2011 - 1280*1024 - Radiosité

Avec 3DSMax 2011 nous mesurons le temps nécessaire au rendu d'une scène 3D. Les résultats sont exprimés en secondes, le processeur le plus rapide a donc la barre la plus... courte ! Pas de surprise nous retrouvons en tête le Core i5 3550 alors que le Pentium G 2120 referme la marche. Les Core i3 ne brillent guère sous 3DSMax. Et ici c'est l'A10-5800K qui reprend l'avantage en étant le deuxième processeur le plus rapide. Toutefois l'avantage par rapport à la génération Llano est minime... à peine 1 seconde de gagnée sur le temps de rendu global.

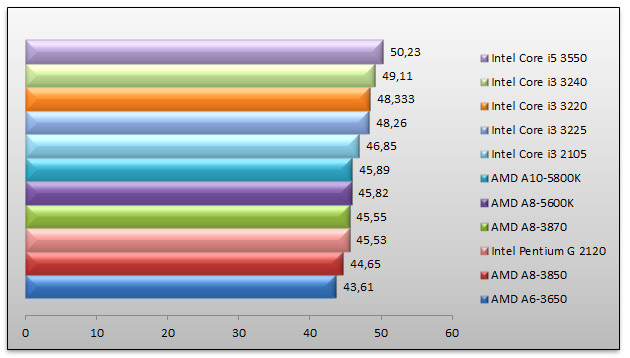

Adobe Photoshop CS6 - Flou radial

Nous utilisons Photoshop CS6 pour appliquer un filtre mutlithreadé sur une image haute résolution. Nous mesurons le temps nécessaire à l'opération. Les résultats sont exprimés en secondes, la barre la plus courte représentant le processeur le plus rapide. Nous vous épargnerons ici le rappel du processeur le plus rapide pour constater que les APU de seconde génération d'AMD figurent parmi les plus véloces. Certes l'A8 devance d'un cheveu l'A10 et certes encore le gain n'est pas évident face aux Llano, mais au moins les nouvelles APU ne sont pas plus lentes ! Et par la même plus rapides que les Core i3 Ivy Bridge... d'une poignée de secondes !

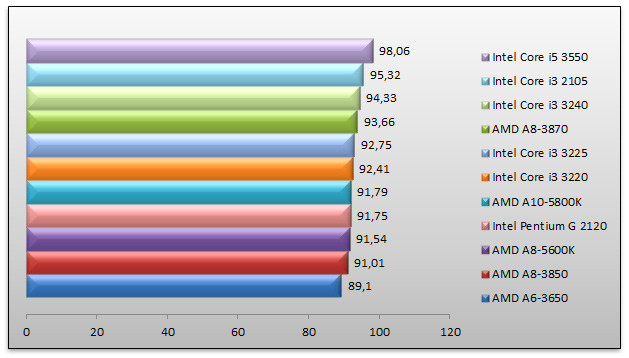

Compression vidéo - MediaCoder

Nous procédons ici à la compression d'un fichier vidéo d'un peu plus de 1 Go de SSD à SSD. Les résultats sont exprimés en secondes, la barre la plus courte représente le processeur le plus rapide. Nos deux extrêmes restent les mêmes : le Pentium G 2120 est affreusement lent quand le Core i5 3550 dépote tout simplement. Bonne nouvelle pour AMD, l'A10 5800K est le plus rapide à cet exercice! On gagne pas loin d'une minute sur l'A8-5600K lors de cette opération. Et face à Llano le gain atteint les 76 secondes. Du coup, les nouvelles APU d'AMD sont plus rapides que les Core i3 : face au Core i3 3220, l'A10-5800K effectue la compression en 176 secondes de moins.

Batman Arkham City - 1920x1080 - DirectX 11

Batman plaide clairement en faveur de l'offre Intel. Les processeurs Core sont en tête et même le Pentium G fait mieux que les processeurs AMD. L'A10-5800K fait ici jeu égal avec le processeur A8-3870 d'ancienne génération. En clair Virgo n'apporte pas de gain notable. Et le plus lent des Core i3, le Core i3 3220 se montre 21% plus rapide que l'A10-5800K. Face au Core i3 2105 d'architecture Sandy Bridge, le Core i3 3220 Ivy Bridge est 5% plus rapide.

Crysis 2 - 1920x1080 - DirectX 11 - Ultra

Crysis 2 est ici utilisé avec FRAPS. Les processeurs Intel Core sont en tête. Pas de surprise. L'A10-5800K se hisse en tête des processeurs AMD les plus rapides, mais face à la précédente génération d'APU le gain est là encore minime : 0,7% en comparant A10-5800K et A8-3870. Plus sensible peut être le gain entre l'A8 5600K et l'A8-3850 de l'ordre de 3%. Et de souligner l'écart nul entre nos deux représentants de la famille Virgo. Reste que le Core i3 2105 fait mieux que la plus rapide des APU AMD, à savoir l'A10 5800K.

Dirt 3 - 1920x1080 - DirectX 11 - Ultra

Les écarts sont bien plus resserrés sous Dirt 3. Le Core i5 3550 se détache, mais c'est peut être le seul. On note du reste que l'A8-3870 de génération Llano fait encore de l'ombre aux nouvelles puces Virgo. Toutefois l'A10-5800K égale le Pentium G 2120 alors que les Core i3 3220/3225 sont un tantinet plus véloces.

Metro 2033 - 1920x1080 - DirectX 11

On termine avec Metro testé en FRAPS toujours. Surprise, l'A8-3870 de génération Llano montre décidément de beaux restes et devance d'un cheveu nos Core i5 3240 et Core i5 3550. Reste que les écarts sont ici minimes. Quant à Virgo, les performances de la nouvelle architecture d'AMD ne sont pas transcendantes : l'A10-5800K et A8-5600K sont en retrait face au Pentium G 2120 (de l'ordre de 1,4%). Du coup Llano donne ici aussi le sentiment d'être un rien plus rapide que Virgo...

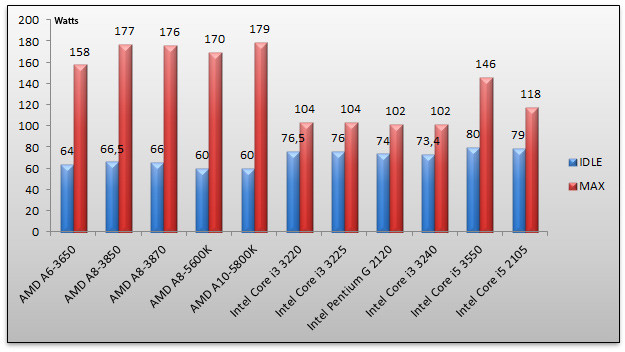

Consommation

Nous avons bien sûr mesuré la consommation électrique de nos processeurs. Pour cela nous employons un wattmètre et nous relevons la consommation électrique du système à la prise. C'est donc la consommation totale de la machine qui est relevée. Nous procédons à deux mesures : au repos sous Windows 7, puis en charge avec Prime 95.

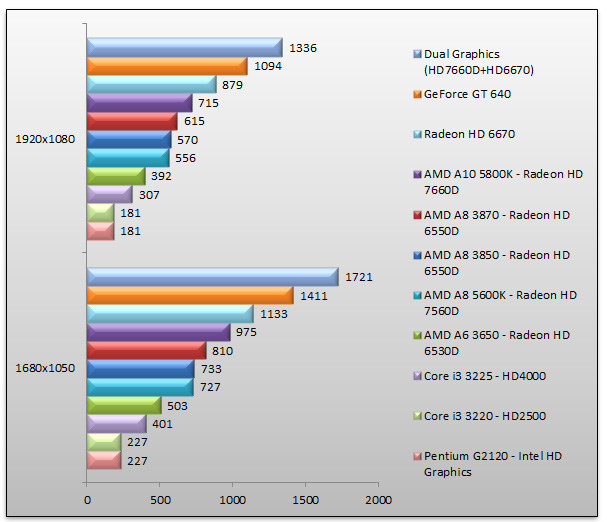

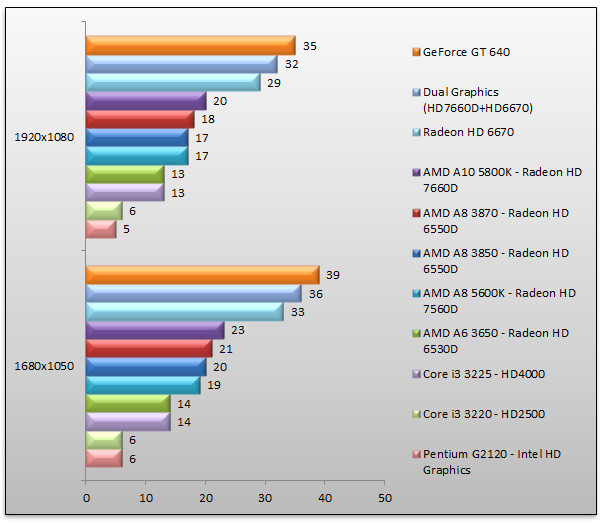

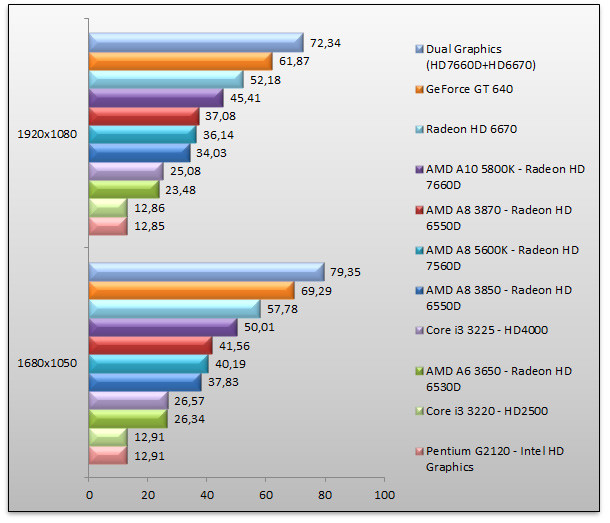

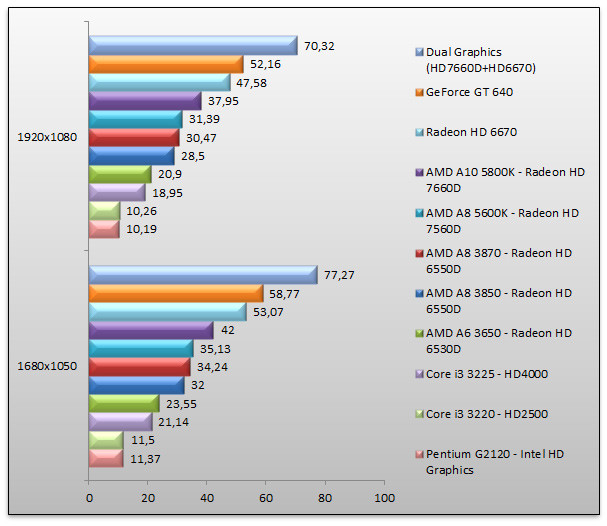

On note la bonne consommation au repos des processeurs AMD : une poignée de watts en moins que leurs homologues Intel. Un bon point qui laissait présager de bonnes choses jusqu'à ce que nous mesurions la consommation.. en charge ! Et là ça ne le fait pas du tout pour AMD. Les nouvelles puces Virgo consomment autant que leurs prédécesseurs Llano et quand un Core i3 3220 consomme en charge 104 Watts, l'A8-5600K engloutit 170 Watts ! À noter les progrès en matière de consommation entre Sandy Bridge et Ivy Bridge : un Core i3 Ivy Bridge consomme en charge moins que son prédécesseur Sandy Bridge, de l'odre de 14 Watts de gagnés entre Core i3 2105 et Core i3 3220.Avec cette seconde génération d'APU, AMD met fort logiquement l'accent sur le graphique intégré. Nous avons donc effectué plusieurs tests pour vérifier les prestations du graphique intégré de Virgo, face à la génération précédente Llano mais aussi face aux processeurs Core i3 d'Intel en architecture Ivy Bridge. Nous retenons deux résolutions de test : le 1680x1050 des écrans 20 pouces et le 1920x1080 des écrans 21,6 pouces et supérieurs qui représentent aujourd'hui la grande majorité de l'offre. Nous utilisons ici des outils de test DirectX 11 et DirectX 10, alors que toutes les solutions retenues sont compatibles DirectX 11. Nous faisons figurer en guise de référence le GeForce GT 640 de NVIDIA testé sur une plate-forme AMD avec processeur A10-5800K alors que nous testons également les prestations du Dual Graphics d'AMD sur la même plate-forme en combinant Radeon HD 7660D et Radeon HD 6670 et en comparant face à une Radeon HD 6670 seule.

3DMark 11 - Performance

Pour 3DMark 11, on observe un gain de performance de l'ordre de 16% entre la génération Virgo et l'ancien Llano. On reste toutefois très loin des performances du GeForce GT 640 seul ou de la solution Dual Graphics qui offrent des performances deux fois supérieures. L'écart de performance du graphique intégré à Virgo est tout de même impressionnant puisque le delta s'élève à 29% entre le Radeon HD 7560D du A8 5600K et le Radeon HD 7660D du A10 5800K. Face au Core i3 3225, muni donc de ce qu'Intel fait de mieux en graphique intégré, AMD offre des performances plus de deux fois supérieures. Sans commentaire donc.

Batman Arkham City - DirectX 11

Avec Batman Arkham City, on observe que le Radeon HD 7660D de l'A10 5800K est ici le plus rapide. Le gain de performances face au Radeon HD 6550D des processeurs Llano s'élève à 9%. Reste que l'on passe de 21 fps à 23 ! Pas de quoi pavoiser. En tête nous retrouvons le GeForce GT 640 et l'on observe que le gain prodigué par le Dual Graphics est de l'ordre de 10%. Quant au HD Graphics d'Intel... voilà.

Dirt 3 - Intermédiaire

Les APU Virgo confirment leurs bonnes prestations. Ici les performances sont acceptables et permettent de jouer modestement. Face au HD 4000 du Core i3 3225, le Radeon HD 7660D du A10 5800K offre des performances 80% supérieures. Tout de même. Le Dual Graphics offre un gain de performances de 38% face à une Radeon HD 6670 seule. A noter l'écart de performance de 24% entre le coeur graphique du Virgo le plus rapide, le modèle A10, et celui du modèle A8. Face à Llano, on gagne au passage 20% de performance.

Far Cry 2

On termine avec Far Cry 2, un titre DirectX 10. Pas de grosse surprise ici. Virgo confirme son avantage sur Llano toujours de l'ordre de 24% alors qu'il écrase Intel et son HD Graphics avec des performances deux fois supérieures. Reste qu'une simple GeForce GT 640 est 37% plus véloce... quant au Dual Graphics il offre ici de jolis gains : 47% !

Conclusion

Du côté du graphique intégré, les progrès sont bien réels. Le gain en performances est manifeste, mais cette fois-ci... à quoi bon ? Si AMD n'a pas de mal à enterrer les performances pour le moins préoccupantes du graphique intégré des Core i3 Ivy Bridge d'Intel, cela ne suffit bien souvent pas pour jouer dans de bonnes conditions aux derniers titres du moment.

Un mot sur l'offre d'Intel justement : les Core i3 Ivy Bridge se montrent convaincants et si leur graphique intégré est toujours aussi poussif, on apprécie l'homogénéité de leurs performances ou encore leur faible consommation. Carton rouge en revanche pour le Pentium G2120 qui franchement nous défrise, tout comme l'écart de prix entre Core i3 3220 et Core i3 3225 qui ne se justifie pas. Les performances graphiques sont certes plus importantes sur le Core i3 3225 mais... pourquoi faire ? A 111 euros, le Core i3 3220 a de sérieux atouts et nous le préférons clairement à l'A10 5800K d'AMD... à condition bien sûr d'avoir recours à une carte graphique. Le Core i3 3240 s'il est le le plus rapide est aussi le plus cher de ces processeurs à près de 140 euros ! C'est hélas trop.

Cet article contient des liens d'affiliation, ce qui signifie qu'une commission peut être reversée à Clubic. Les prix mentionnés ainsi que les marchands mis en avant sont susceptibles d'évoluer afin de toujours vous proposer le meilleur prix sur le produit concerné.

Lire la charte de confiance

Lire la charte de confiance