Vous avez sans doute déjà entendu parler de ARM, les petites puces qui colonisent nos téléphones. Mais qu’en est-il de RISC-V ?

Une révolution à bas bruit commence à prendre forme dans le petit monde des gadgets connectés. Après des années de domination sans pareil sur le marché, ARM, le fabricant qui détient les droits d’exploitation sur la quasi-intégralité des processeurs de smartphones, tablettes, montres connectées et même de quelques ordinateurs, est enfin challengée par un nouveau venu.

En effet, Qualcomm va lancer sa toute première puce RISC-V dans un futur proche. Vous n’avez pas tout compris ? Pas de panique, on vous explique.

ARM ? RISC-V ? C'est quoi ?

Dans l’immense majorité de nos appareils mobiles se trouvent des processeurs qui sont tous construits plus ou moins de la même manière : en respectant l’architecture ARM. Ces processeurs ARM, qui sont plus simples et moins gourmands en énergie que les processeurs Intel, que l’on trouve dans nos PC, sont construits en respectant le cahier des charges de l’entreprise Arm ltd, qui détient les droits sur cette manière spécifique de fabriquer des processeurs mobiles.

Que ce soit nos téléphones, nos montres connectées ou même les nouveaux ordinateurs d’Apple avec leurs puces Silicon, tout ce beau monde utilise des puces ARM. Le terme est pratiquement devenu un synonyme de puce mobile, tant les appareils portables qui n’utilisent pas cette technologie sont rares. Problème, construire une puce ARM signifie donc payer des droits à l’entreprise du même nom. Qualcomm en particulier, qui fournit les processeurs de bon nombre de mobiles Android, passe très souvent à la caisse. D'autres entreprises, comme Intel, investissent carrément dans la société.

La bataille pour les entrailles d'Android

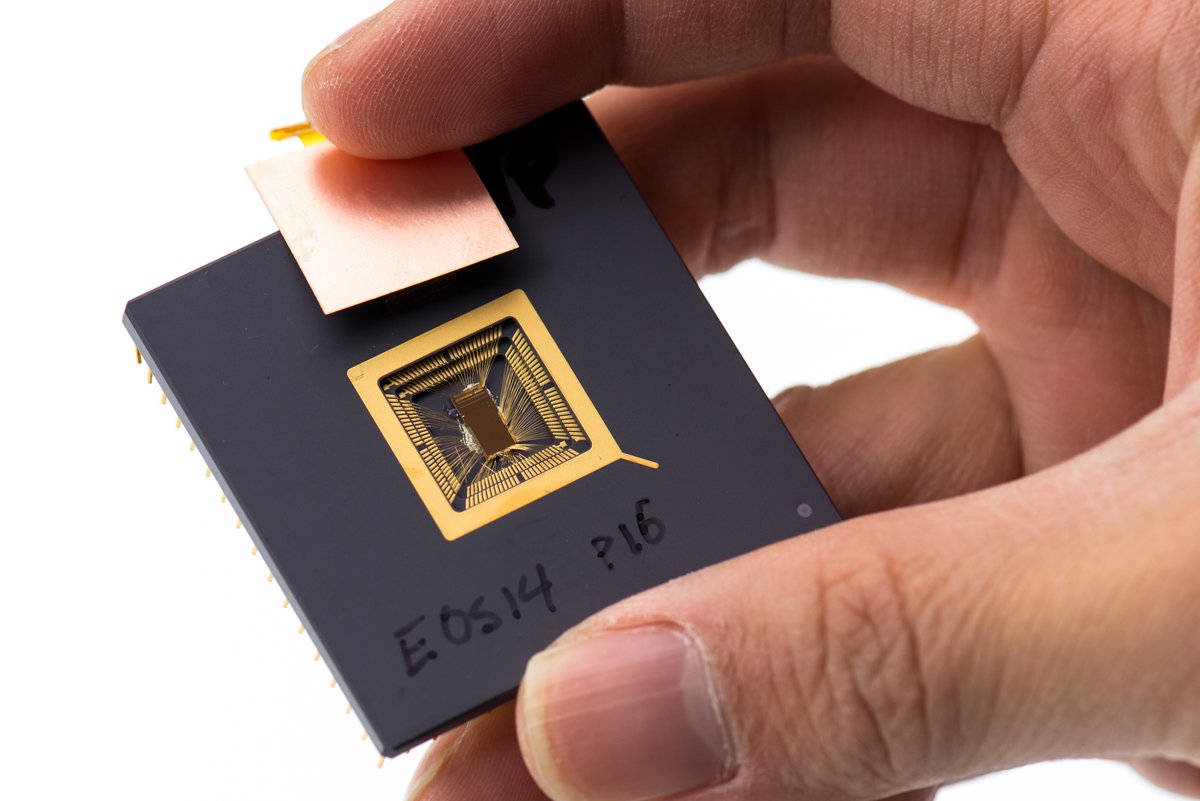

C’est pourquoi l’entreprise a annoncé la sortie de son tout premier processeur RISC-V dans un communiqué de presse publié le 17 octobre. RISC-V est une architecture concurrente à ARM qui a l’énorme avantage d’être ouverte et libre… et donc gratuite à utiliser. Cela signifie que des constructeurs de mobiles pourraient utiliser des processeurs RISC-V dans des smartphones sans avoir rien à payer à personne. Et les premiers résultats sont plutôt encourageants.

Si ces puces sont déjà utilisées dans certains appareils, l’architecture n’a encore jamais été déployée sur des appareils très grand public. C’est en cela que l’annonce de Qualcomm est importante. Elle marque le début d’un changement profond qui pourrait venir bouleverser la domination d'Arm dans le monde d’Android. Google est d’ailleurs à fond derrière ce projet, puisque l’entreprise a annoncé en janvier 2023 avoir commencé le travail pour adapter Android à RISC-V. Apple aussi travaille là-dessus.

Il y a encore beaucoup de travail, et même Qualcomm y va petit à petit. L’entreprise se lance d’abord sur un processeur de smartwatch, et pas de smartphones, mais la bataille pour les entrailles de nos appareils mobiles est bel et bien lancée avec cette annonce.

Source : Qualcomm