19

Intel a dévoilé hier ce qui s'impose comme le plus grand FPGA au monde : le Stratix 10 GX 10M. Gravé en 14 nm, ce circuit programmable embarque la bagatelle de 43,3 milliards de transistors et 10,2 millions de cellules logiques. De quoi distancer le Virtex UltraScale+ VU19P et ses 35 milliards de transistors. Annoncé en août par l'américain Xilinx, ce dernier se limitait à « seulement » 9 millions de cellules logiques et se basait sur une gravure en 16 nm.

Au jeu de celui qui sortira le plus gros FPGA, Intel vient de mettre un soufflet à son concurrent Xilinx. Avec son Stratix 10 GX 10M, le groupe de Santa Clara met à profit son système EMIB (Embedded Multi-die Interconnect Bridge) pour assembler deux grands dies FPGA et quatre chiplets émetteur-récepteurs sur un seul circuit. Cette technologie avait notamment été utilisée par Intel pour ses puces Kaby Lake-G. Abandonnées par les bleus en octobre, celles-ci couplaient, pour rappel, un processeur Intel à un iGPU AMD Radeon RX Vega, le tout saupoudré de mémoire vidéo HMB2.

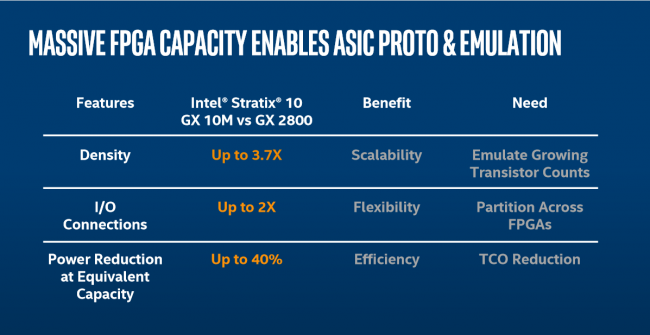

Ce procédé d'assemblage de différents composants sur un circuit unique permet à Intel de doter son FPGA de 10,2 millions de cellules logiques et 2 304 ports I/O. C'est presque quatre fois plus d'éléments que ce que comporte le Stratix 10 GX 2800 (2,75 millions de cellules logiques et 1 160 connections I/O au compteur), l'ancien FPGA d'Intel. Mais au juste... c'est quoi un FPGA ?

Un FPGA, qu'est-ce que c'est et à qui ça sert ?

Xilinx nous donne, sur son site officiel, une bonne définition de ce qu'est un FPGA (Field Programmable Gate Arrays ou Réseau de Portes Programmables, en français). Il s'agit en fait de semiconducteurs articulés autour d'une matrice de blocs logiques configurables (CLB), liés les uns aux autres par des interconnexions programmables.Le principal intérêt d'un circuit FPGA est qu'il permet d'être programmé en fonction d'une application ou fonctionnalité particulière, et ce après être sorti d'usine. Cette flexibilité, explique Xilinx, permet par exemple de distinguer les FPGA des ASIC (Application Specific Integrated Circuits), qui sont pour leur part conçus pour des tâches spécifiques... et ne peuvent donc pas être reconfigurés.

La nature évolutive des FPGA les rend particulièrement utiles dans des secteurs de pointe, comme l'aérospatial, la défense, le monde automobile, celui des serveurs, ou encore le domaine des télécommunications.

Intel enterre le Stratix 10 GX 2800, son ancien modèle de FPGA

Mais revenons à l'annonce. Pour mieux démontrer l'avancée technologique proposée par son Stratix 10 GX 10M, Intel a comparé son nouveau FPGA à pas moins de quatre Stratix 10 GX 2800. De quoi illustrer une réduction colossale de 40 % de consommation, et ce à capacité et fréquences équivalentes.Comme l'indique Tom's Hardware, Intel procède différemment de Xilinx pour connecter les dies de son nouveau produit. Au lieu de compter, comme son concurrent, sur un interposeur, le groupe utilise (et nous l'avons évoqué plus haut) sa technologie EMIB 2.5D, qui permet une bande passante copieuse entre les deux dies qui composent le Stratix 10 GX 10M. Intel évoque ainsi un bus doté d'un maximum de 25 920 connexions, chacune disposant d'un débit de 2 Gb/s. La bande passante inter-dies s'élève ainsi à un seuil de 6,5 To/s.

43,3 milliards de transistors : une estimation... à la louche

Très fier d'évoquer les 43,3 milliards de transistors peuplant son nouveau circuit, Intel prend tout de même soin de préciser qu'il s'agit là d'une estimation basée sur la taille des dies du Stratix 10 GX 10M, et sur leur densité. Chacun de ces dies mesure ainsi près de 1 400 mm², pour une densité estimée à plus ou moins 31MTr / mm².Nous avons là le plus gros circuit logique du marché... Et il n'est gravé qu'en 14 nm. Même la gamme Xilinx Versal (gravée en 7 nm) se limite actuellement à 37 milliards de transistors. Tandis que chez NVIDIA le V100, recèle 21,2 milliards de transistors sur un die de 815 mm², souligne Tom's Hardware.

Reste enfin la question du lancement de ce Stratix 10 GX 10M. Sur ce point, Intel évoque une mise sur le marché d'ici quelques mois pour son nouveau FPGA, sans se montrer beaucoup plus précis.

Source : Tom's Hardware